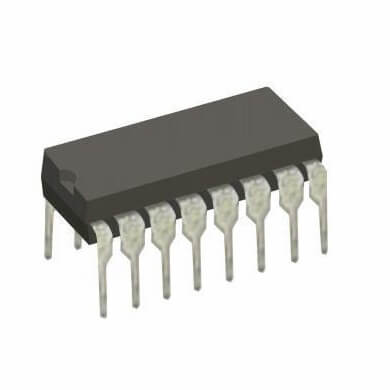

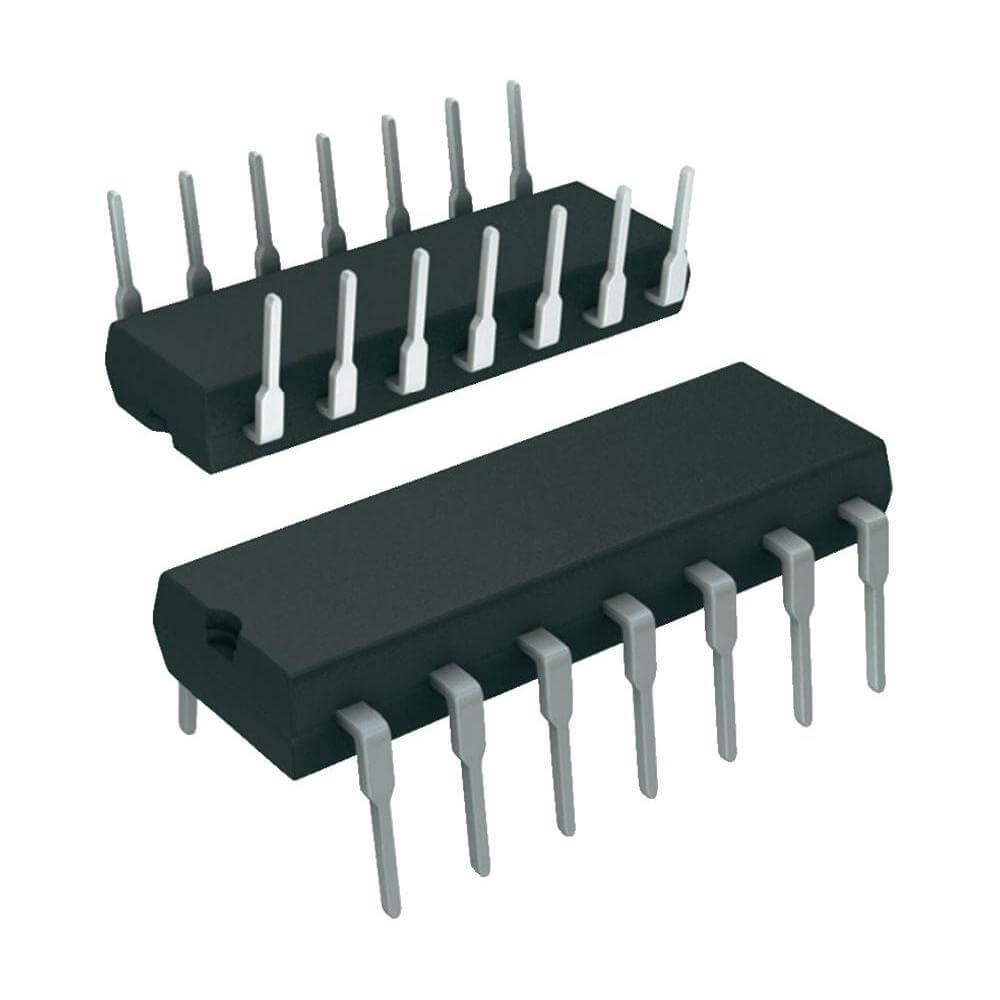

74161 عبارة عن عداد ثنائي متزامن قابل للضبط مسبقًا مع حمل داخلي للرأس. يتم توفير التشغيل المتزامن من خلال تسجيل جميع النعال في وقت واحد على الحافة الإيجابية للساعة (CP). قد تكون مخرجات العدادات (Q0 إلى Q3) مضبوطة مسبقًا على "عالية" أو "منخفضة". يؤدي انخفاض مستوى الإدخال الموازي (PE) إلى تعطيل إجراء العد ويؤدي إلى تحميل البيانات عند مدخلات البيانات (D0 إلى D3) في العداد الموجود على الحافة الإيجابية للساعة. يتم إجراء الإعداد المسبق بغض النظر عن المستويات عند مدخلات تمكين العد (CEP وCET). يقوم LOW عند مدخل إعادة الضبط الرئيسي (MR) بتعيين Q0 إلى Q3 LOW بغض النظر عن المستويات عند منافذ الإدخال CP وPE وCET وCEP (وبالتالي توفير وظيفة واضحة غير متزامنة). تعمل ميزة النظرة المستقبلية على تبسيط التسلسل التسلسلي للعدادات. يجب أن يكون كل من CEP وCET عاليًا ليتم احتسابهما. يتم تغذية مدخلات CET إلى الأمام لتمكين إخراج العد الطرفي (TC). وبالتالي فإن خرج TC الذي تم تمكينه سوف ينتج نبضة خرج عالية لمدة تساوي تقريبًا خرجًا عاليًا قدره Q0. يمكن استخدام هذا النبض لتمكين المرحلة المتتالية التالية. يتم تحديد الحد الأقصى لتردد الساعة للعدادات المتتالية بواسطة تأخير نشر CP إلى TC ووقت إعداد CEP إلى CP، وفقًا للصيغة التالية:

وتشمل المدخلات الثنائيات المشبك. وهذا يتيح استخدام المقاومات المحددة الحالية لواجهة المدخلات

الفولتية الزائدة عن VCC.

سمات

؟ يتوافق مع معيار JEDEC رقم. 7 أ

؟ مستويات إدخال CMOS

؟ العد والتحميل المتزامن

؟ 2 عدد تمكين المدخلات لتسلسل n-بت

؟ إعادة تعيين غير متزامن

؟ حافة إيجابية أثارت على مدار الساعة

؟ حماية البيئة والتنمية المستدامة:

؟ HBM JESD22-A114F يتجاوز 2000 فولت

؟ MM JESD22-A115-A يتجاوز 200 فولت

؟ خيارات حزمة متعددة

؟ محدد من -40 درجة مئوية إلى 85 درجة مئوية و -40 درجة مئوية إلى 125 درجة مئوية

تحميل ورقة البيانات

- لا يمكن إضافة "4049 IC "Hex Buffer/Converter"" لسلة مشترياتك لأن المنتج غير متوفر في المخزون.

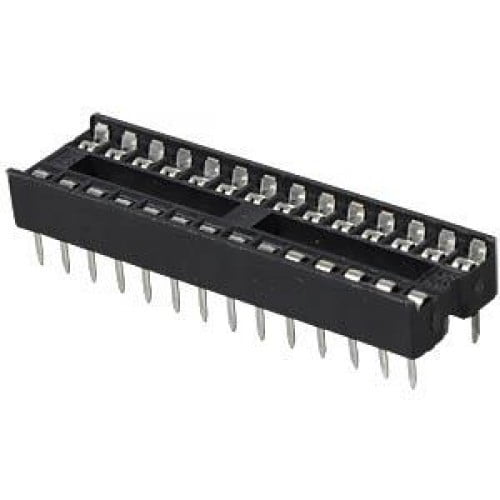

قاعدة IC ذات 28 دبوسًا

3.50 جنية

مكثف كهربائيا 4.7 فائق التوهج 250 فولت

1.60 جنية

74161 عداد ثنائي متزامن قابل للضبط مسبقًا 4 بت

27.00 جنية

74161 "عداد ثنائي متزامن 4 بت؟" إعادة تعيين غير متزامن "؟ في حزمة 16-DIP.

رمز المنتج:

IC_74161

التصنيفات: 74 سلسلة, الدوائر المتكاملة المتكاملة