The 7476 is an high speed CMOS DUAL J-K FLIP FLOP WITH CLEAR fabricated with silicon gate C2MOS technology. Depending on the logic level applied to J and K inputs, this device changes state on the negative going transition of clock input pulse (CK). The clear function is accomplished independently of the clock condition when the clear input (CLR) is taken low. All inputs are equipped with protection circuits against static discharge and transient excess voltage.

Features

* HIGH SPEED : fMAX = 80MHz (TYP.) at VCC = 6V

* LOW POWER DISSIPATION: ICC =2mA(MAX.) at TA=25?C

* HIGH NOISE IMMUNITY: VNIH = VNIL = 28 % VCC (MIN.)

* SYMMETRICAL OUTPUT IMPEDANCE: |IOH| = IOL = 4mA (MIN)

* BALANCED PROPAGATION DELAYS: tPLH @ tPHL

* WIDE OPERATING VOLTAGE RANGE: VCC (OPR) = 2V to 6V

* PIN AND FUNCTION COMPATIBLE WITH 74 SERIES 73

Download Datasheet

- You cannot add "POT 5 kohm 1/2W Horizontal Square Cermet Potentiometer" to the cart because the product is out of stock.

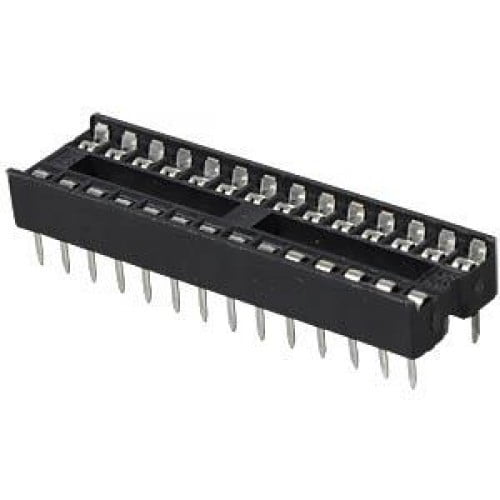

28 Pin IC Base

3.50 EGP

Electrolytic Capacitor 4.7uF 250v

1.60 EGP

7476 Dual JK Flip Flop with Preset and Clear

30.00 EGP 22.00 EGP

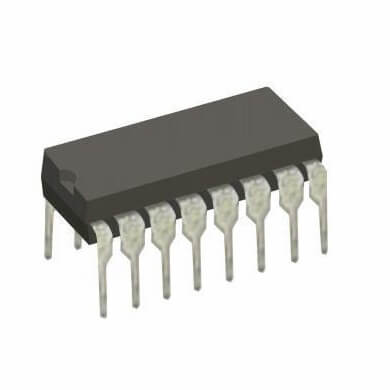

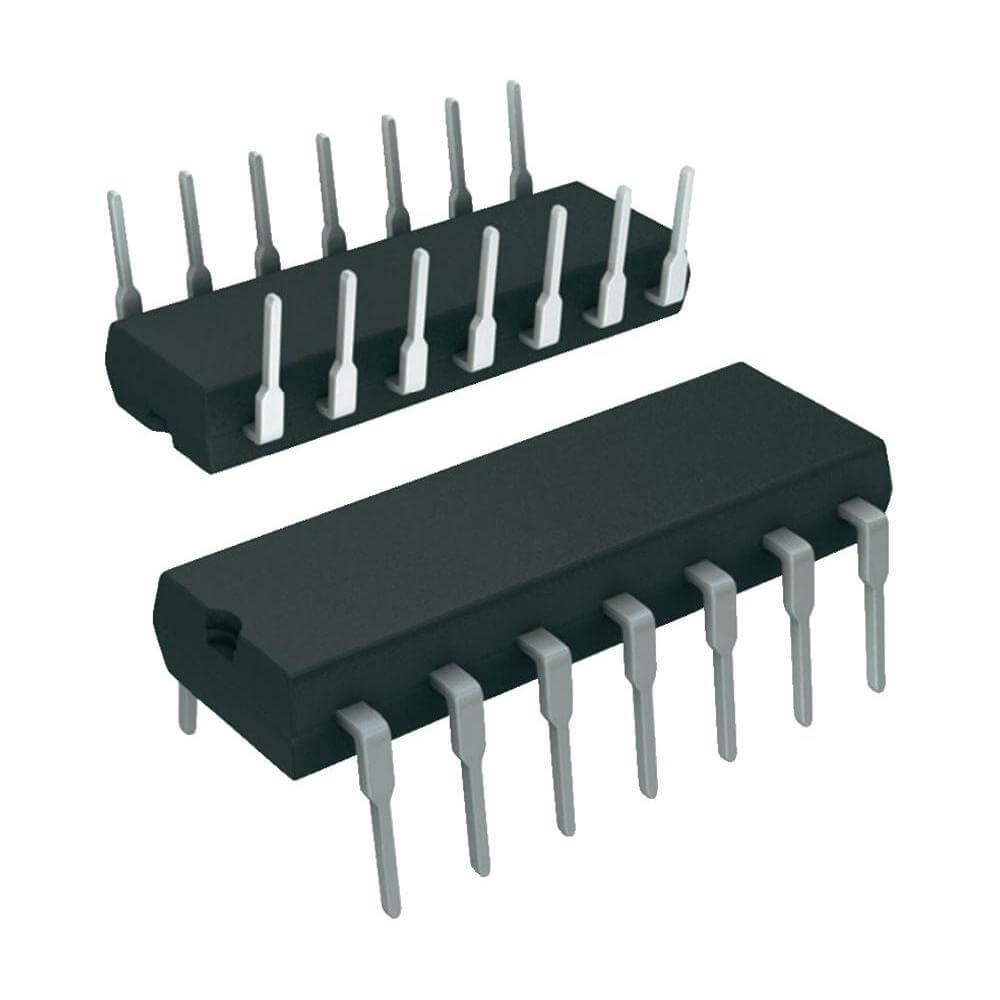

7476 is a Dual J-K Flip Flop with Preset and Clear ? In 16-DIP Package.

SKU:

IC_7476

Categories: 74 Series, Integrated Circuits ICs